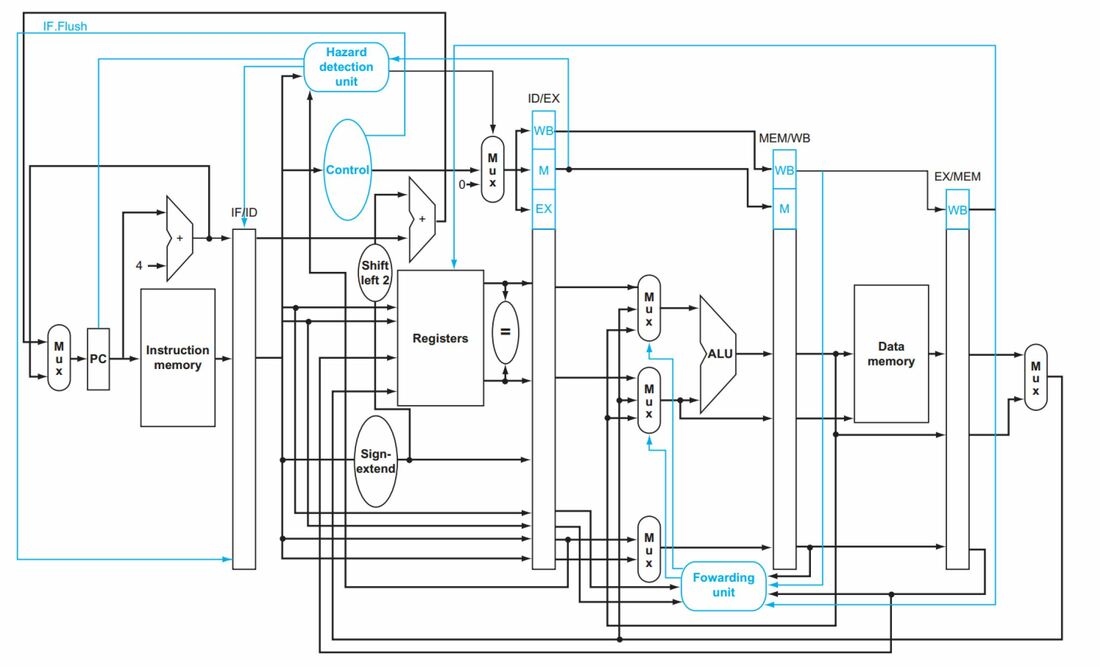

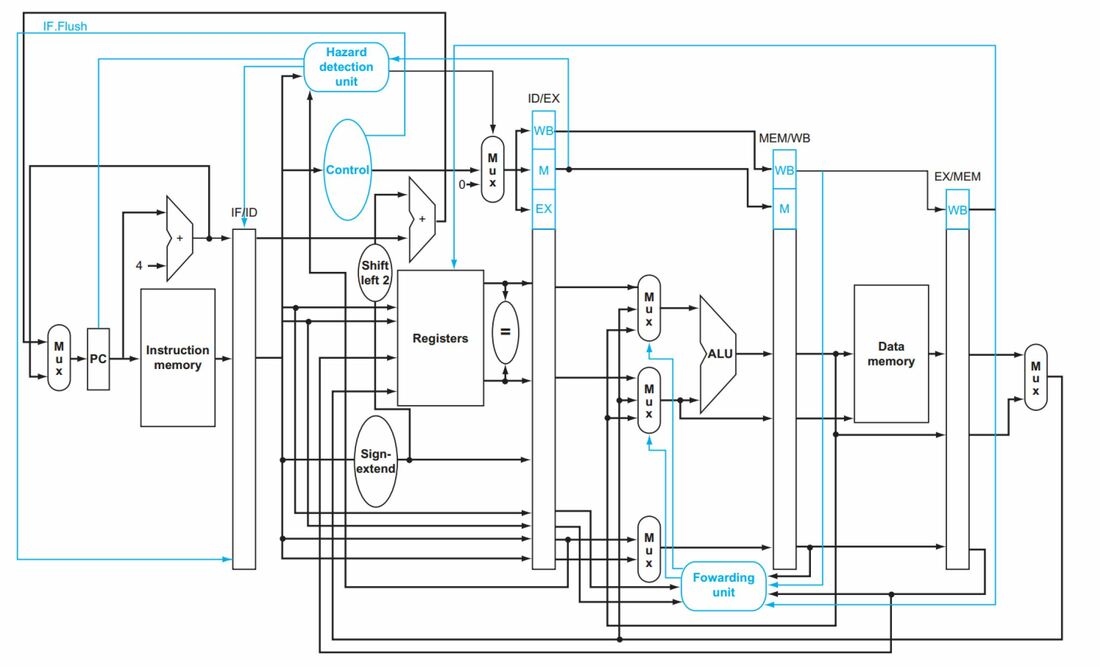

In this project, I built a MIPS microprocessor using VHDL code. There are two different versions of MIPS microprocessor implemented: (1)Single Clock Single Instruction (2)Multiple Clock Single Instruction (Pipelined) MIPS Microprocessor. I will be focusing on showing the pipeline MIPS Microprocessor here as it is more related to real life implementation.

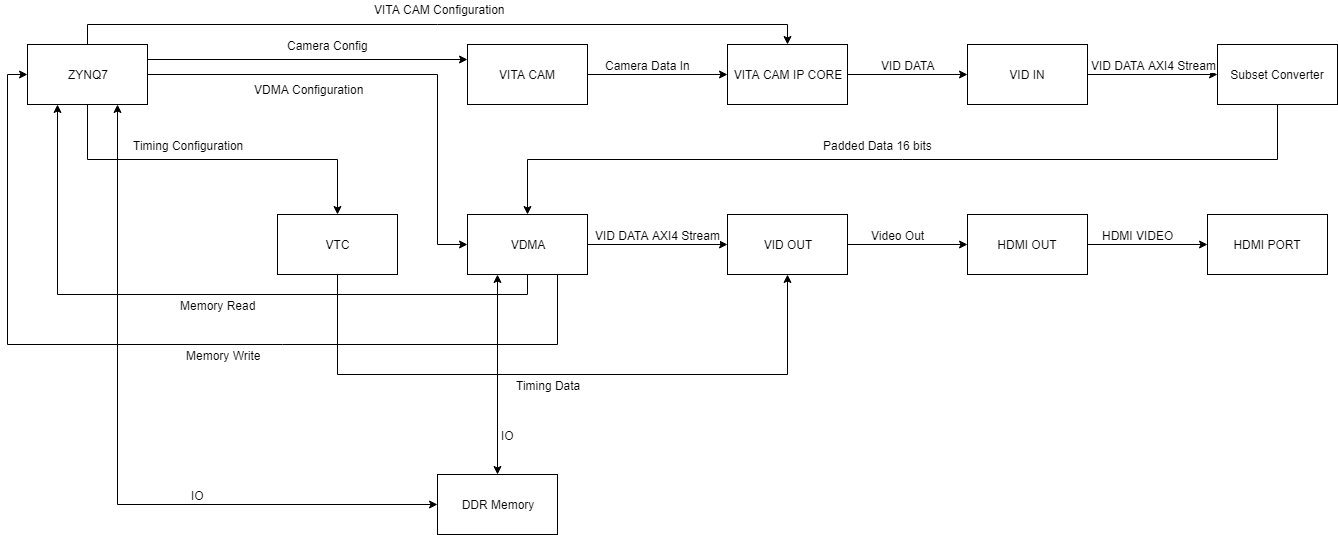

System Block Diagram:

Introduction:

Introduction:

In this project, we are implementing a 5-stage pipelined MIPS processor. The architecture shall support at least 6 MIPS standard instructions: ADD, ADDI, LW, SW, BEQ, J. Many of the components of processor are provided but primarily focuses would be understanding and connecting the whole pipeline processor using components given as well as building our own hazard detection, forwarding unit, branch comparator and setting up the main control.

For detailed software simulation results, please refer project write-up document above.

Skills & Knowledge Gained:

- Building a MIPS Pipelined and non-pipelined Microprocessor using ALU, Register, and Memory VHDL Files provided.

Resources:

- ModelSim

- Computer Organization And Design 5th Edition Textbook

- Quartus Prime (Optional)

- Pipeline Registers (if_id.vhd, id_ex.vhd, ex_mem.vhd, mem_wb.vhd)

- VHDL Sources (adder_32.vhd, ALU.vhd, and_2.vhd, branch_comparator.vhd, dmem.vhd, forwarding_unit.vhd, hazard_detection_unit.vhd, imem.vhd, main_control.vhd, mipsprocessor_pipe.vhd, mux4to1_32bit.vhd, mux21_1bit.vhd, mux21_5bit.vhd, mux21_32bit.vhd, pc_reg.vhd, register_file.vhd, sign_externder_16_32.vhd, sll_2.vhd)

Introduction:

Introduction: