Name: Joseph Ward, Yao Jiang Cheah, Raed Ibrahim

## CprE 488 - Embedded Systems Design

MP-1: QUAD UAV INTERFACING

1. (Part 2: First Flight) In your writeup, describe your experiences in practicing controlling the quad.

It was very hard to control the airplane, it seems that you need to trim it and calibrate it very well, but I would say it was a very fun and rewarding experience.

2. (Part 3: Trainer Port) In your writeup, describe the PPM signals. What do each of the channels correspond to, and what are their minimum and maximum ranges? What is the total length of the individual PPM frames, and what is the minimum length of the idle pulse?

-Each PPM Frame is 20ms and each channel is a pulse in that 20 ms frame.

Channel 1 is 1.5 ms out of that frame and the idle pulse is at min 0.4ms and the second channel is 0.8 ms and the third channel is 1ms and the 4th channel is 1.25 ms with the 5th channel as 2ms and the 6th channel 1.75ms.

Mainly You have a PPM Generate signal and a PPM capture signal. The generate basically generates PPM frames which have the required channels and then transmits then in the form of highs and lows and then the PPM capture basically takes these highs and lows and from them into the required Frame. The meaning of these frames is that the remote controller has different channels and lengths for these buttons and to transmit them to determine what is pressed.

3. (Part 3: Trainer Port) Based on the ZedBoard documentation and your oscilloscope measurement of the trainer port, what concerns do you have about making this connection?

Mainly we would need a Level Shifter To connect the pins from the trainer port to the Pmods on the board and supplying the right voltage which should be  $3.3~\rm v$ .

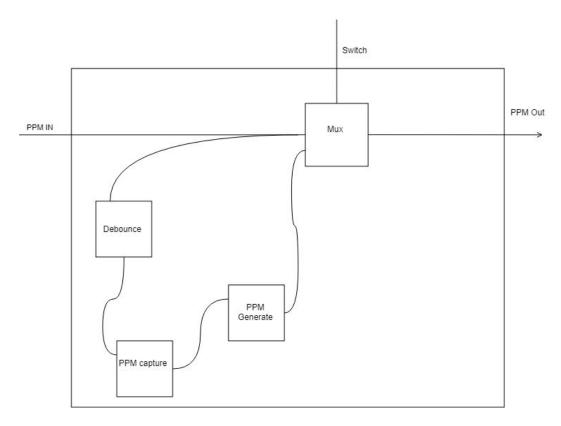

## 4. (Part 5: System and IP Creation)

a. In your write up, provide a structural diagram of the axi\_ppm design, from the top-level AMBA AXI interface down to where you user logic will reside.

b. How does an address on the AMBA bus generate a read or write enable signal for the slave registers in your design?

In our design, we use a signal called "channel" to save the state that we are in, and these states represent the channel that we are in. "channel" then initiates the the save to the right register.

c. How will you PPM state machine get access to the IP core's Memory Mapped registers

We have two sub modules in the Axi PPm module that interact with that, PPM generate and PPM capture, For the PPM Capture we use all the registers from the VHDL Code within the submodule itself while the PPM Generate uses the registers from the PPM AXI module itself. After that we can write and read to the registers from our SDK by calling them with their address and offset .

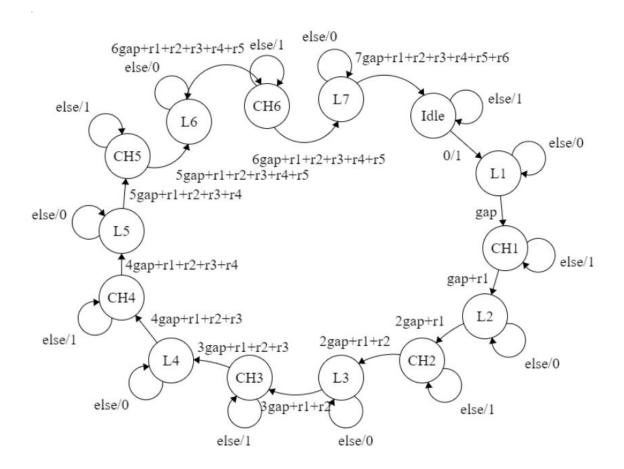

5. (Part 5: System and IP Creation) Starting from the generic FSMs in your HW-1 write-up, update the User Logic module such that the design can appropriately capture and generate PPM values for the Hobby King 6ch transmitter as described above.

## Generate\_ppm FSM:

For the Mealy's state machine below:

- Each gap represent 40000 decimal values at the counter. (E.g. 7gap = 7\*40000 counter values)

- Unknown r1, r2, r3, r4, r5, r6 represent the 6 different registers value taken from the software.

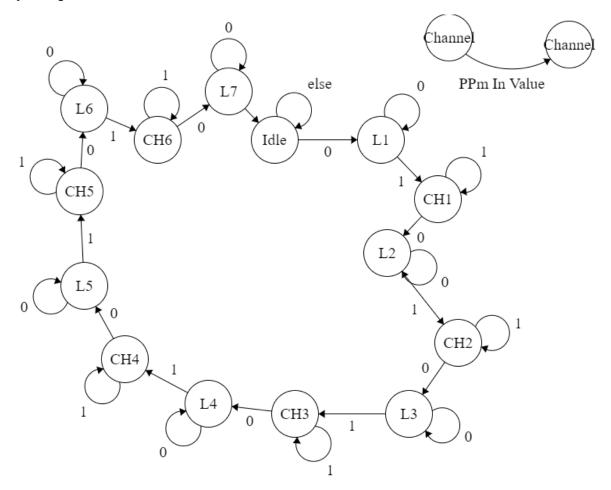

## Capture PPM:

We have a signal called Channel that saves the State we are in so that in our clock process we can know which capture register to count to.